序列存在檢測

此條目翻譯自其他語言維基百科,需要相關領域的編者協助校對翻譯。 |

此條目可參照英語維基百科相應條目來擴充。 (2023年3月9日) |

序列存在檢測(英語:serial presence detect,縮寫SPD)[1]是一種訪問記憶體模組有關訊息的標準化方式。 早期的72 pin SIMM包括五個針腳,提供5位元平行存在檢測(PPD)資料,而168 pin DIMM標準更改為序列存在檢測,以編碼更多訊息。[2]

在普通的現代電腦開機時,它將進行一次開機自檢(POST)。自從20世紀90年代中期以來,這個過程包括自動設置當前存在的硬件。SPD是一項記憶體硬件特性,可使電腦了解存在的記憶體以及訪問記憶體要使用的時序。

部分電腦可以完全自動地適應硬件變更。在大多數情況下,有一個特殊的可選步驟可以訪問BIOS參數,得以檢視並可能更改相關設置。有些電腦可以控制如何使用SPD中儲存的資料——可以選擇性的修改記憶體時序,乃至完全覆蓋(忽視)SPD資料,詳見超頻。

儲存的訊息

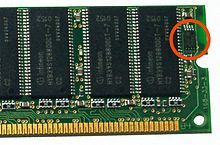

[編輯]對於支援SPD的記憶體模組,JEDEC標準要求在記憶體模組的一個EEPROM上的低128位元組中存有特定參數。這些位元組包括模組相關的時序參數、製造商、序列號及其他實用訊息。利用記憶體的裝置可以讀取該訊息來自動確定模組的關鍵參數。例如,SDRAM模組上的SPD資料可能提供有關CAS潛伏時間的訊息,使系統可以自動組態而無需用戶干預。

SPD EEPROM採用SMBus訪問,這是I²C協定的一個變種。這將模組上的通訊針腳數量減少到兩個:時鐘訊號和資料訊號。EEPROM與RAM共用接地針腳,有自己的電源針腳,並有三個額外針腳(SA0-2)來標識該槽,用於將EEPROM分配到0x50-0x57範圍內的唯一地址。通訊線路不僅可以在8個記憶體模組之間共用,同一SMBus通常也用於主機板上的系統健康監控任務,例如讀取電源電壓、CPU溫度和風扇速度。

(如果沒有防寫,SPD EEPROMs也響應I²C地址0x30–0x37。一個擴充使用0x18–0x1F地址訪問可選的晶片上溫度感測器。[3])

SDR SDRAM

[編輯]

第一個SPD規範由JEDEC發佈,並由英特爾加強,作為其PC100記憶體規範的一部分。[4]指定的大多數值為二進碼十進數形式。最重要的半位元組可以包含10到15個值,並在某些情況下可以擴充到更高。在這種情況下, 1、2、3的編碼用於編碼16,17和18。最高的0的半位元組被保留表示為「未定義」。

SPD ROM定義了最多三個DRAM時序,在位元組18中用設置位指定了三個CAS延遲。首先是最高的CAS延遲(最快時鐘),然後是兩個降低時鐘速度的較低的CAS延遲。

DDR2 SDRAM

[編輯]DDR2 SPD標準做了一些修改,但大致同上。一個顯着變化是刪除混亂且很少使用的有兩個不同大小Rank的DIMM支援。

時間周期欄位(位元組9、23、25和49)以二進碼十進數(BCD)編碼,一些額外編碼以十分位定義,以正確表示一些常見時序:

DDR3 SDRAM

[編輯]DDR3 SDRAM標準大幅修繕,簡化了SPD內容佈局。取代多個BCD編碼的納秒欄位,一些「時基」單元被規定為高精度,並且各種時序參數被編碼為基本單元的倍數。[5]此外,根據CAS延遲指定不同時序的做法已被刪除,現在只有一組時序參數。

修訂1.1使一些參數列示為「中等時基」值加上(帶符號,-128 +127)「精細時基」校正。通常來說,中等時基為1/8 ns(125 ps),精細時基為1、2,5或5 ps。為了與缺少校正的早期版本相容,中等時間基數通常向上取整,並且校正為負。以這種方式工作的值為:

模組的儲存容量可以從位元組4、7和8計算。模組寬度(位元組8)除以每個晶片的位數(位元組7)得出每個rank的晶片數量。然後可以乘以每個晶片的容量(位元組4)和模組上晶片的Rank數量(通常為1或2,從位元組7)。

DDR4 SDRAM

[編輯]擴充

[編輯]JEDEC標準僅規定了部分SPD位元組。真正關鍵的資料放在了前64個位元組[6][7][8][9][10],而其餘部分則由製造商標定。然而,通常提供的EEPROM為256位元組。剩餘空間目前已有一些用途。

增強效能組態(EPP)

[編輯]記憶體通常在SPD ROM中附有保守的時序建議,以確保在所有系統上基本功能執行正常。愛好者通常會花費很多時間來手動調整記憶體時序以提高速度。

增強效能設定檔是一項SPD擴充,由Nvidia和Corsair開發,其中包含使DDR2 SDRAM以更高效能執行的額外訊息,例如JEDEC SPD規範中不包括的供電電壓和命令時序訊息。EPP訊息儲存在同一個EEPROM中,不過位元組在99-127,屬於DDR2 SPD標準中的未使用區域。[11]

這些參數專為nForce 5、nForce 6和nForce 7晶片組上的記憶體控制器設計。Nvidia鼓勵在BIOS為其高端主機板晶片組支援EPP。此能旨在提供「一鍵超頻」,以最小的努力取得更佳效能。

Nvidia為效能和穩定性得到認證的EPP記憶體提供的名稱是「SLI-Ready 記憶體」。[12]術語「SLI-Ready 記憶體」引起了一些混亂,因為這與NVIDIA SLI無關。用戶可以使用單個影片卡(哪怕非Nvidia卡)搭配EPP/SLI記憶體,也可以在沒有EPP/SLI記憶體的情況下執行多卡SLI影片組態。

其擴充版本EPP 2.0則支援DDR3記憶體。[13]

Extreme Memory Profile(XMP)

[編輯]與之類似的是,英特爾為DDR3 SDRAM DIMM開發了一個JEDEC SPD擴充。它使用JEDEC未分配的位元組176-255來編碼更高效能的記憶體時序。中文也稱「擴充記憶體組態」[14] 頭部包含下列資料。其中最重要的是「中等時基」值MTB,它是一個合理的納秒(常用值為1/8、1/12和1/16 納秒)。之後的許多時序值都以整數個MTB單位表示。

頭部還包括該設定檔旨在支援的每個記憶體通道的DIMM數量;更多的DIMM可能無法正常工作。

AMD也開發了一個SPD擴充集名為AMP,功用與XMP一樣。[15]

供應商指定記憶體

[編輯]一種常見的濫用是將訊息寫入某些記憶體區域,以將特定供應商的記憶體模組繫結到特定系統。已知富士通技術解決方案有這樣做。向系統添加不同的記憶體模組通常會導致拒絕執行或其他反制措施(例如每次啟動時需按F1)。

02 0E 00 01-00 00 00 EF-02 03 19 4D-BC 47 C3 46 ...........M.G.F 53 43 00 04-EF 4F 8D 1F-00 01 70 00-01 03 C1 CF SC...O....p.....

這是一個美光科技512 MB記憶體模組的輸出,它的品牌是富士通西門子,注意「FSC」字串。該系統BIOS拒絕從偏移128h開始沒有此訊息的記憶體模組。

讀取和寫入SPD訊息

[編輯]記憶體模組製造商會將SPD訊息寫入模組上的EEPROM。主機板BIOS則讀取SPD訊息來組態記憶體控制器。在大多數(但不是所有)主機板晶片組中,存在多個能讀取和修改SPD訊息的程式。

- dmidecode(頁面存檔備份,存於互聯網檔案館)程式可以解碼記憶體(及其他)有關訊息,可以在Linux、FreeBSD、NetBSD、OpenBSD、BeOS、Cygwin和Solaris上執行。dmidecode不直接訪問SPD訊息;它會報告有關記憶體的BIOS資料。[16]此訊息可能受限或不正確。

- 在Linux系統上,用戶空間程式decode-dimms可以以i2c-tools[17][18]解碼和印出電腦中任何有SPD訊息的記憶體訊息。它需要內核中支援SMBus控制器、EEPROM內核驅動,並且SPD EEPROM已連接到SMBus。在舊的Linux發行版上,decode-dimms.pl作為lm_sensors的一部分可用。

- OpenBSD自4.3版本起包含驅動程式spdmem(4)[永久失效連結]來提供有關記憶體模組的訊息。該驅動程式從NetBSD移植(自5.0版本可用)。

- Coreboot讀取和使用SPD訊息來初始電腦中的所有記憶體控制器的時序、大小及其他屬性。

- Windows上使用如HWiNFO32[19]、CPU-Z或Speccy軟件可以讀取和顯示SPD中的DRAM模組訊息。

使用eeprom編程器硬件和軟件直接訪問記憶體的EEPROM,可以直接讀寫SPD訊息,而無需關心晶片組。

對於舊手提電腦來說,一種不太常見的用法是通用的SMBus讀取器,因為BIOS可以在讀取後禁用模組上的內部EEPROM,因此匯流排基本上可以使用[需要解釋]。所用方法是將A0、A1線拉低,使內部記憶體關閉,從而允許外部裝置訪問SMBus。完成此操作後,客製化的Linux版本或DOS應用程式就可以訪問外部裝置。這樣做的一個常見目的是從LCD面板的記憶體晶片中恢復資料,將通用面板改裝為手提電腦專用。

在舊裝置

[編輯]部分較舊的裝置必需使用具有平行存在檢測(常稱為簡單存在檢測,或縮寫PD)的SIMM。這些裝置中部分使用非標準的PD編碼,尤其是如IBM電腦、惠普LaserJet,及其他一些印表機。

參見

[編輯]參考資料

[編輯]- ^ JEDEC发布DDR3串行存在检测规格文档. EDN電子技術設計. 2011-09-05 [2017-05-07]. (原始內容存檔於2019-02-21).

- ^ Thomas P. Koenig; Nathan John, Serial Presence Detection poised for limelight, Electronic News, 1997-02-03, 43 (2153) [2017-05-07], (原始內容存檔於2015-05-03)

- ^ JEDEC Standard 21-C section 4.1.4 "Definition of the TSE2002av Serial Presence Detect (SPD) EEPROM with Temperature Sensor (TS) for Memory Module Applications"

- ^ Application note INN-8668-APN3: SDRAM SPD Data Standards (頁面存檔備份,存於互聯網檔案館), memorytesters.com

- ^ Understanding DDR3 Serial Presence Detect (SPD) Table. [2017-05-07]. (原始內容存檔於2015-12-22).

- ^ JEDEC Standard 21-C section 4.1.2.4 (頁面存檔備份,存於互聯網檔案館) "SPDs for DDR SDRAM"

- ^ JEDEC Standard 21-C section 4.1.2.10 (頁面存檔備份,存於互聯網檔案館) "Specific SPDs for DDR2 SDRAM"

- ^ JEDEC Standard 21-C section 4.1.2.11 "Serial Presence Detect (SPD) for DDR3 SDRAM Modules"

- ^ JEDEC Standard 21-C section 4.1.2 (頁面存檔備份,存於互聯網檔案館) "SERIAL PRESENCE DETECT STANDARD, General Standard"

- ^ JEDEC Standard 21-C section 4.1.2.5 (頁面存檔備份,存於互聯網檔案館) "Specific PDs for Synchronous DRAM (SDRAM)"

- ^ DDR2 UDIMM Enhanced Performance Profiles Design Specification (PDF), Nvidia, 2006-05-12 [2009-05-05], (原始內容存檔 (PDF)於2020-02-21)

- ^ SLI-Ready Memory with Enhanced Performance Profiles One-Click Hassle-Free Memory Performance Boost (PDF). [2017-05-07]. (原始內容存檔 (PDF)於2020-02-21).

- ^ Enhanced Performance Profiles 2.0 (頁面存檔備份,存於互聯網檔案館) (pages 2–3)

- ^ Intel Extreme Memory Profile (Intel XMP) DDR3 Technology (PDF). [2017-05-07]. (原始內容存檔 (PDF)於2010-01-05).

- ^ AMD 平台也有 XMP 記憶體超頻,這是怎麼一回事?. [2018-06-11]. (原始內容存檔於2020-11-05).

- ^ dmidecode: What's it good for?. [2017-05-07]. (原始內容存檔於2011-05-22).

- ^ decode-dimms Perl program. [2017-05-07]. (原始內容存檔於2008-12-02).

- ^ I2CTools – lm-sensors. Lm-sensors.org. [2014-08-14]. (原始內容存檔於2012-03-11).

- ^ HWiNFO32. [2017-05-07]. (原始內容存檔於2020-12-11).

外部連結

[編輯]- Serial Presence Detect Standard, General Standard

- SPD Rev1.0 for DDR SDRAM(頁面存檔備份,存於互聯網檔案館)

- SPD Rev1.2 for DDR2 SDRAM(頁面存檔備份,存於互聯網檔案館)

- SPD Rev1.3 for DDR2 SDRAM

- SPECIALITY DDR2-1066 SDRAM(頁面存檔備份,存於互聯網檔案館)

- Linux軟件套件i2c-tools

- Instructions on how to use lm-sensors or i2c-tools to read the data

- Memory Performance: 16GB DDR3-1333 to DDR3-2400 on Ivy Bridge IGP with G.Skill(頁面存檔備份,存於互聯網檔案館) – explanation of various timing values