反相器

| 基本邏輯閘 | |

| 緩衝 | 非 |

| 及 | 反及 |

| 或 | 或非 |

| 異或 | 同或 |

| 蘊含 | 蘊含非 |

| 輸入 A |

輸出 NOT A |

| 0 | 1 |

| 1 | 0 |

反相器(英語:Inverter)也稱非門(英語:NOT gate),是數字邏輯中實現邏輯非的邏輯門,功能見右側真值表。

這種功能代表了數字電路中理想開關表現的假定,但是在實際的反相器設計中,元件有其需要特別關注的電氣特性。實際上,CMOS反相器的非理想過渡區表現使其能在模擬電路中用作A類功率放大器(如作為運算放大器的輸出級[1])。

概述

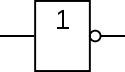

[編輯]下列包括邏輯門的3種符號:形狀特徵型符號(ANSI/IEEE Std 91-1984)、IEC矩形國標符號(IEC 60617-12)和不再使用的DIN符號(DIN 40700)。其他的邏輯門符號見邏輯門符號表。

| 表達式 | 符號 | 功能表 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE Std 91-1984 | IEC 60617-12 | DIN 40700 | ||||||||

|

|

|

| |||||||

電路實現

[編輯]-

NMOS反相器

-

PMOS反相器

-

TTL反相器

-

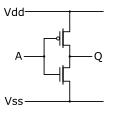

靜態CMOS反相器

-

飽和負載數字反相器

-

三極管反相器

-

開關實現的反相器

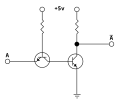

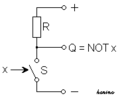

反相器電路輸出電壓所代表的邏輯電平與輸入相反。反相器可以僅用一個NMOS晶體管或一個PMOS連接一個電阻來構建。因為這種「阻性漏極」方式只需要使用一種類型的晶體管,其製造成本非常小。不過,由於電流以兩種狀態之一流過電阻,這種阻性漏極配置有功耗和狀態改變的處理速率問題。另外,反相器可以用兩個互補晶體管配置成CMOS反相器。這種配置可以大幅降低功耗,因為在兩種邏輯狀態中,兩個晶體管中的一個總是截止的。處理速率也能得到很好的提高,因為與NMOS型和PMOS型反相器相比,CMOS反相器的電阻相對較低。反相器也可以電阻-晶體管邏輯(RTL)或晶體管-晶體管邏輯(TTL)使用雙極性晶體管(BJT)構建。

數碼電子電路在邏輯0和1(二進制)對應的固定電壓電平範圍內進行運算。反相器電路是基本的邏輯門,可以在兩個電壓電平間變換。實際構建的反相器的電壓都是不同的,例如TTL電路中0是低電平,+5V是高電平。

數字功能模塊

[編輯]

反相器是數字電路中的一種基本功能模塊。將兩個串行反相器的輸出作為一位寄存器的輸入就構成了鎖存器。鎖存器、數據選擇器、譯碼器和狀態機等精密數字元件都需要使用基本反相器。

六反相器是一種包含6個反相器的集成電路。例如,7404 TTL芯片有14個引腳,4049 CMOS芯片有16個引腳,兩種芯片都各有2個引腳用於電源供電/基準電壓,12個引腳用於6個反相器的輸入和輸出(4049有2個引腳懸空)。[2]

性能測定

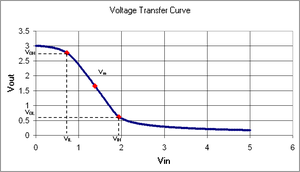

[編輯]反相器性能常用表示輸入-輸出電壓關係的電壓傳輸特性曲線(VTC)來測定。曲線圖能反映出元件的參數,包括噪聲容限、增益和操作邏輯電平。

反相器理想化的電壓傳輸特性曲線是單位階躍函數,這表明反相器能在高電平和低電平間無延遲精確的翻轉,但在實際元件中,曲線存在過渡區。曲線表明若輸入為低電壓,則輸出為高電壓;若輸入為高電壓,則輸出電壓逐漸接近0V。過渡區的斜率是性能測量的指標,過渡區越陡峭,即斜率越大,性能越好,若斜率接近無窮,則電路能在高電平和低電平間精確翻轉,反相器就是理想的。

噪聲容限可以通過每一工作區中的最大輸出電壓VOH和最小輸入電壓VIL的比值來測定。

輸出電壓VOH可以在級聯多個元件時測定信號驅動強度。

參考文獻

[編輯]- ^ Intersil數據表:CA3130 BiMOS運算放大器 (頁面存檔備份,存於網際網路檔案館)和CA3160 BiMOS運算放大器 (頁面存檔備份,存於網際網路檔案館)

- ^ Texas Instruments:4049 CMOS六反相緩衝器/轉換器 (頁面存檔備份,存於網際網路檔案館),數據表:[1] (頁面存檔備份,存於網際網路檔案館)

| ||||||||

| ||||||||||||||