单片系统

此條目可参照英語維基百科相應條目来扩充。 |

单片系统或片上系统(英語:System on a Chip,縮寫:SoC)是一个将電腦或其他电子系统集成到单一芯片的集成电路[1]。单片系统可以处理数字信号、模拟信号、混合信号甚至更高频率的信号。单片系统常常應用在嵌入式系统中[2]。单片系统的集成规模很大,一般达到几百万门到几千万门。[3]

尽管微控制器通常只有不到100kB的随机存取存储器,但是事实上它也是一台小電腦的結構,一种简易的、功能弱化的单芯片系统,而一般認知的“单片系统”这个术语常被用来指功能更加强大的处理器,这些处理器可以运行Windows和Linux的某些版本。单片系统更强的功能要求它具备外部存储芯片,例如有的单片系统配备了闪存。单片系统往往可以连接额外的外部设备。单片系统对半导体器件的集成规模提出了更高的要求。为了更好地执行更复杂的任务,一些单片系统采用了多个处理器核心。[4]:1

基本架构

[编辑]

典型的单片系统具有以下部分:

- 至少一个微控制器或微处理器、数字信号处理器,但是也可以有多个中央控制核心

- 記憶體则可以是唯讀記憶體、随机存取存储器、EEPROM和闪存中的一种或多种

- 用于提供时间脉冲信号的振盪器和锁相环电路

- 由计数器和计时器、电源电路组成的外部设备

- 不同标准的连线接口,如通用串行总线、火线、以太网、通用异步收发和序列周邊介面等

- 用于在数字信号和模拟信号之间转换的模拟数字转换器和数字模拟转换器

- 电压调理电路以及稳压器

数据的流动主要借助了系统中的I/O总线,例如安謀國際科技公司的高级微控制器总线架构。采用DMA控制器,则可以使得外部数据直接被传送到存储器,无需经过中央处理器,这可以大大改善数据吞吐的效率。

设计流程

[编辑]

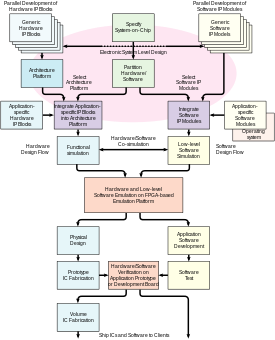

一个完整单片系统由硬件和软件两部分组成,其中软件用于控制硬件部分的控制器、微处理器或数字信号处理器核心以及外部设备和接口。单片系统的设计流程主要是其硬件和软件的设计。

由于单片系统的集成度已经达到数百万门,工程师必须尽可能采取可重用的设计思路。大部分的单片系统都使用了预定义的半导体知识产权核(IP核,包括软核、硬核和固核),以可重用设计的方式来完成快速设计。与以往的集成电路设计相比,可重用设计要求设计人员的工作更加标准化,例如规范的代码书写风格等等。[4]:4-5[4]:68-110设计人员需要关注硬件驱动程序的实现,从而实现具体的功能。协议栈是一个重要的概念,它与诸如通用串行总线的接口的工业标准有关。设计人员通常使用计算机辅助工程工具来把已经设计(或者购买)的核连接在一起,这时集成开发环境可以被用来整合包含不同子功能的模块。

设计的芯片在被送到工厂进行硬件工艺制造之前,设计人员会采取不同方式对芯片的逻辑功能进行验证。功能验证的重要性丝毫不亚于集成电路设计,对于现代的超大规模集成电路,这一步骤在整个设计周期中将花费相当的时间和金錢。[5]为了应对芯片极高的复杂程度,类似SystemVerilog、SystemC、e验证语言和OpenVera的硬件验证语言逐渐变得流行。在验证阶段,系统软件的程序错误可以被反馈到设计人员那里,以便进行针对性的修正。

工程师通常会使用精心设计的仿真器或者在通用的现场可编程逻辑门阵列(FPGA)上运行程序,来测试之前进行的系统级、行为级(或用另一个术语寄存器传输级,即RTL)的设计代码,这一步的目的是在设计项目在进行最后的硬件生产(投片)之前,其软、硬件的功能、性能得到最后的确认,并改正所有功能、时序、功耗上的错误。

其中,使用现场可编程逻辑门阵列构建产品原型的工作方式可以让工程师评估、测试各种刺激(stimulus)施加在系统时,系统的运行状态。相关的电子设计自动化工具包括Certus[6],它可以被用来分析、检测系统设计的寄存器传输级代码,监视其中的变量和信号在整个运行过程中的变化。

在功能验证过程结束之后,工程师还会采取计算机辅助工程的方式完成布局、布线流程,这一步他们需要关注何种布局布线方式可以尽可能地减少连线之间的信号干扰和延迟,功率也是另外一个考虑的重点。[4]:42-46

参考文献

[编辑]- ^ Atlantic. Encyclopedia Of Information Technology. Atlantic Publishers & Dist. 13 June 2007: 461– [30 January 2013]. ISBN 978-81-269-0752-6.

- ^ Ian Grout. Integrated Circuit Test Engineering: Modern Techniques. Springer. 2006: 225– [30 January 2013]. ISBN 978-1-84628-173-0.

- ^ 虞希清. 专用集成电路设计实用教程. 浙江大学出版社. : 3. ISBN 978-7-308-05113-2.

- ^ 4.0 4.1 4.2 4.3 Michael Keating, Pierre Breacaud. 片上系统——可重用设计方法学(第二版)(英文名:Reuse Methodology Manual for System-on-a-Chip Designs, Third Edition). 北京: 电子工业出版社. 2004. ISBN 7-5053-9338-3.

- ^ Is verification really 70 percent?. Eetimes.com. [2009-08-12].[永久失效連結]

- ^ Tektronix hopes to shake up ASIC prototyping. EE Times. 2012-10-30 [2012-10-30].[永久失效連結]

相关条目

[编辑]

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||